핵심 요약 (Executive Summary)

- 키워드: CNFET 양산 성공, MIT-ADI 공동 연구, 70년 실리콘 신화 붕괴, 에너지 효율 10배, 미국 주도 패권 재편

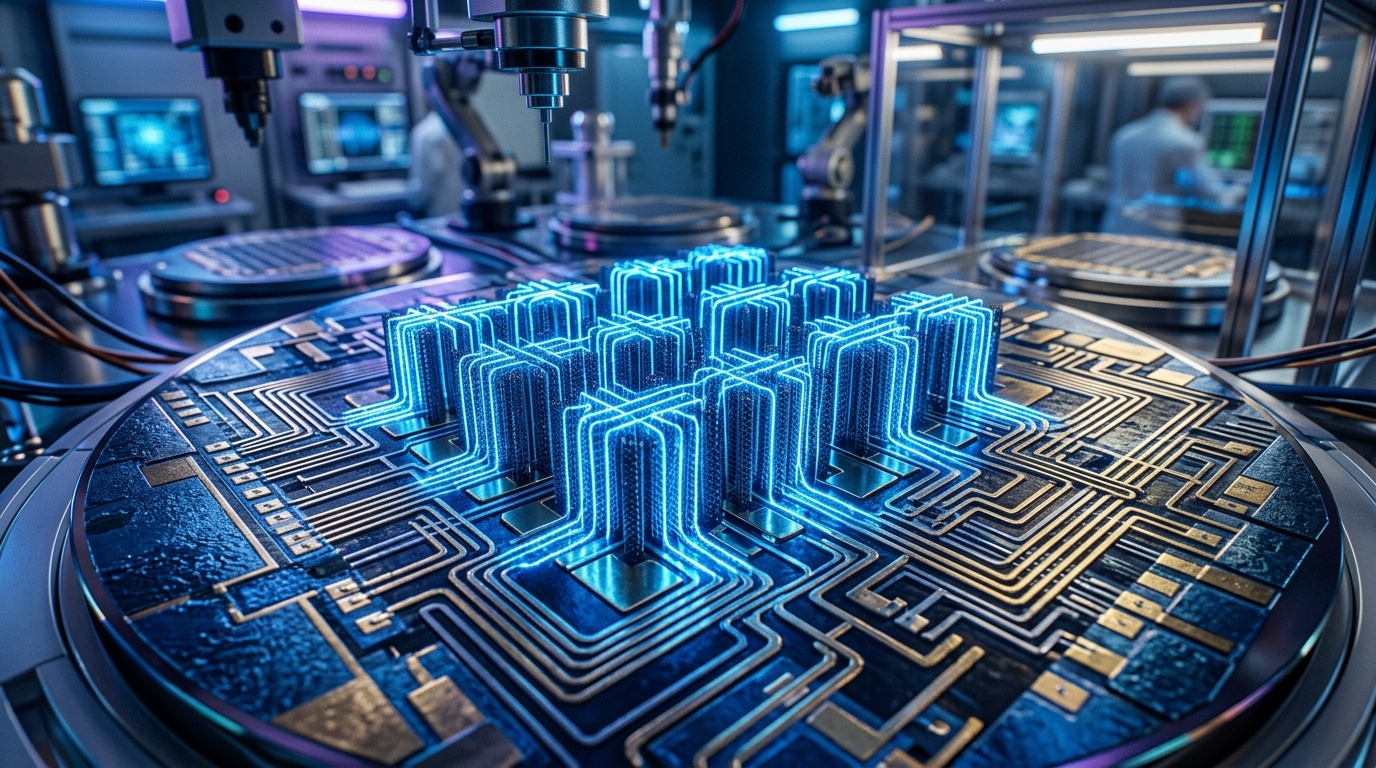

- 요지: 최근 MIT와 아날로그디바이스(ADI)가 기존 실리콘 파운드리 시설을 활용한 **’탄소 나노튜브(CNFET) 웨이퍼 자동화 제조 공정’**에 성공하며 상용화의 문턱을 넘었습니다. 이는 1nm 이하 공정에서 실리콘의 물리적 한계를 극복할 유일한 대안이 실험실을 벗어나 양산 단계에 진입했음을 의미합니다.

- 임팩트: 동일 전력 대비 10배 이상의 연산 성능 확보, AI 데이터센터 및 전기차 시장의 전력 효율 혁명, 한국 주도의 실리콘 미세 공정 전략에 대한 근본적인 위협.

반도체 산업을 70년간 지배해온 실리콘(Si)의 시대가 황혼기를 맞이하고 있습니다. 삼성전자와 TSMC가 2nm를 넘어 1nm 공정으로 진입하려 할 때 직면하는 ‘퀀텀 터널링’과 ‘누설 전류’ 문제는 더 이상 실리콘만으로는 해결할 수 없는 물리적 벽이 되었습니다. 채널 폭이 원자 몇 개 수준으로 얇아지는 1nm 영역에서는 전자가 장벽을 뚫고 지나가는 현상이 발생해 제어가 불가능해지기 때문입니다.

이러한 한계를 돌파할 ‘포스트 실리콘’ 시대의 주인공이 바로 탄소 나노튜브 전계효과 트랜지스터(CNFET)입니다. 최근 공개된 최신 동향에 따르면, CNFET는 단순한 연구 수준을 넘어 상업용 웨이퍼 제조 공정의 표준화를 목전에 두고 있습니다.

1. [최신 동향] MIT-ADI, CNFET 양산 자동화 공정 확립

그동안 CNT 반도체의 최대 난제는 ‘대량 생산’이었습니다. 나노미터 단위의 탄소 튜브를 웨이퍼 위에 정밀하게 배치하는 작업이 극히 어려웠기 때문입니다. 하지만 최근 MIT와 아날로그디바이스(ADI) 연구팀은 기존의 실리콘 파운드리 시설과 장비를 그대로 활용하면서도 웨이퍼 전체에 CNT를 고르게 증착하는 **’자동화된 웨이퍼 스케일 제조 공정(Automated Wafer-scale Fabrication)’**을 입증하는 데 성공했습니다. (출처: 글로벌이코노믹/Nature)

주요 혁신 포인트:

1) 상용 장비 호환성: 특수한 신규 장비 도입 없이 기존 반도체 라인을 활용하여 비용 효율적인 전환이 가능해졌습니다.

2) 결함 제어 기술: 금속성 CNT를 99.9999% 제거하여 반도체로서의 순도를 확보하는 공정 자동화가 완성되었습니다.

3) 에너지 효율 혁명: 동일 성능 대비 실리콘 칩보다 에너지 효율을 최대 10배까지 높일 수 있어, 전력 고갈 위기의 AI 데이터센터에 결정적인 해법을 제시합니다.

2. CNFET가 만드는 구조적 혁신과 1nm의 벽 돌파

CNFET는 직경이 1~2nm에 불과한 원통형 구조로, 그 자체로 완벽한 ‘채널’ 역할을 수행합니다. 실리콘 원자 크기가 약 0.2nm인 상황에서 1nm 공정 설계는 사실상 소재의 물리적 한계치에 도달한 것이지만, CNT는 이를 구조적으로 극복합니다.

구조적 우위:

– 초박막 바디(Ultra-thin Body): CNT의 극도로 작은 직경은 게이트가 채널을 완벽하게 감싸는 GAA 구조 구현에 최적화되어 있어, 1nm 이하에서도 누설 전류를 완벽하게 차단합니다.

– 탄도성 수송(Ballistic Transport): 전자가 불순물과 충돌하지 않고 이동하는 성질 덕분에 에너지 손실이 거의 없으며, 실리콘 대비 3배 이상의 연산 속도를 보장합니다. (출처: Duke University Research)

3. 소재 패권의 이동: 미국 주도의 생태계 재편

이번 MIT의 양산 성공은 한국 반도체 산업에 실존적인 위협이 되고 있습니다. 삼성전자와 SK하이닉스가 실리콘 위에서 나노 단위 공정을 깎는 노하우로 세계를 지배해왔으나, 판 자체가 ‘탄소’로 바뀌면 기존의 노광/식각 공정 자산은 순식간에 구시대의 유물이 될 수 있기 때문입니다.

전략적 변화:

– 미국 중심의 표준화: 소재와 설계 도구(EDA)를 선점한 미국이 제조 공정의 표준까지 장악하게 될 경우, 제조 기술력만으로 버티던 파운드리 시장의 주도권이 급격히 이동할 수 있습니다.

– 인텔의 역습: 인텔은 이미 2027년 ’10A(1nm급)’ 공정 진입을 선언하며 새로운 소자 구조 도입을 암시했으며, 이번 MIT의 성과와 맞물려 탄소 기반 양산 체제 구축에 박차를 가할 것으로 보입니다.

전략적 인사이트 (Strategic Insight)

단기: 1nm 공정의 시나리오가 ‘실리콘 최적화’에서 ‘소재 전환(CNT)’으로 급격히 선회하고 있습니다. 중기: AI 가속기 및 저전력 HPC 시장을 중심으로 CNFET 기반의 하이브리드 칩이 상용화될 전망입니다. 장기: 누가 먼저 탄소 기반 양산 생태계를 구축하느냐가 향후 70년의 반도체 패권을 결정할 최후의 승부처가 될 것입니다.